Hello,

I have a question on how to use the teddyreg filter at higher voltages with LSK170 /LSJ74 FETs.

The application would be, for example, but not limited to the Hackernap frontend.

The LSK170 hasa 40V breakdown limit from gate to drain/source, the LSJ74 has a 25V limit.

My first excercices with LTspice show that at startup the gate voltage doesn´t rise fast enough to stay below the 25V (and 40V) limit of the FETs.

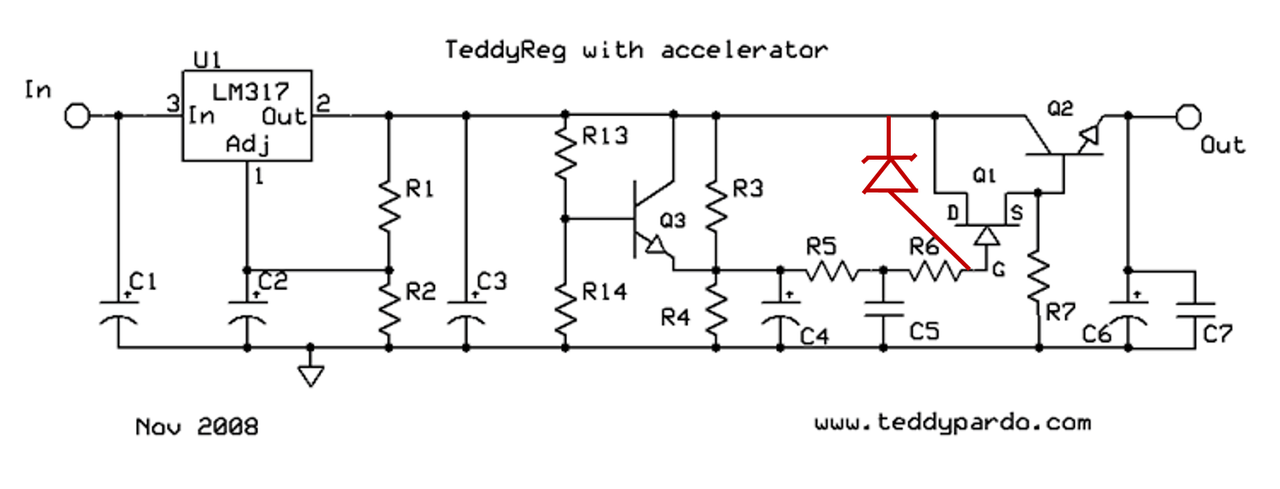

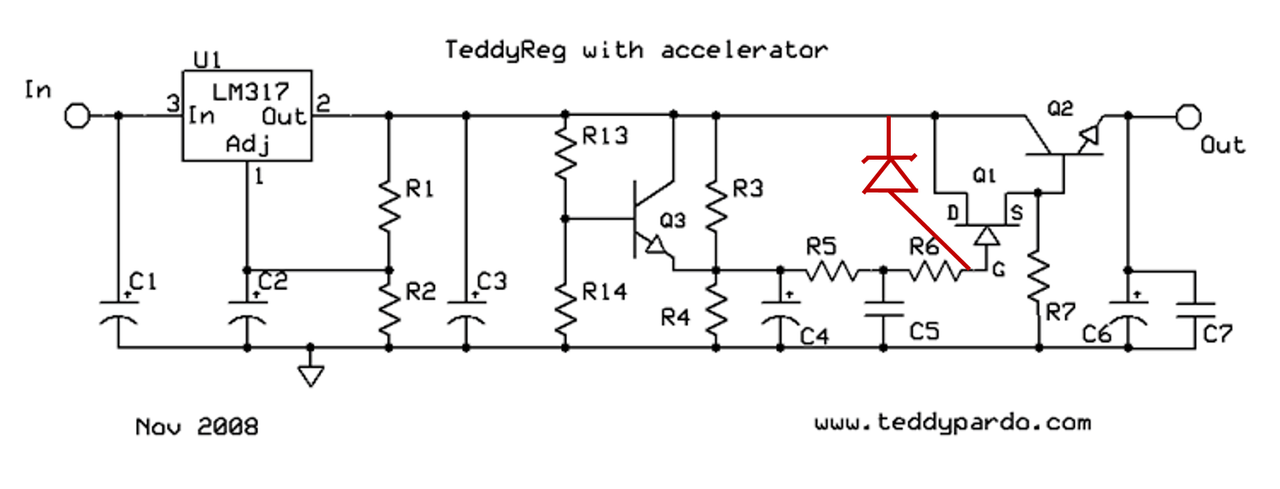

My thinking was to just use a Zener diode with e.g. 15V breakdown as shown here:

The zener diode would maintain a maximum of 15 V across drain and gate during startup and else be practically invisible, because the d/g voltage is far below 10 V in regular operation.

LTspice says it might work as intended, but since I am not an electrical engineer and haven´t seen this anywhere I would like to have this sanity checked from folks that know what they are doing. Are there any drawbacks?

Thanks

Florian

I have a question on how to use the teddyreg filter at higher voltages with LSK170 /LSJ74 FETs.

The application would be, for example, but not limited to the Hackernap frontend.

The LSK170 hasa 40V breakdown limit from gate to drain/source, the LSJ74 has a 25V limit.

My first excercices with LTspice show that at startup the gate voltage doesn´t rise fast enough to stay below the 25V (and 40V) limit of the FETs.

My thinking was to just use a Zener diode with e.g. 15V breakdown as shown here:

The zener diode would maintain a maximum of 15 V across drain and gate during startup and else be practically invisible, because the d/g voltage is far below 10 V in regular operation.

LTspice says it might work as intended, but since I am not an electrical engineer and haven´t seen this anywhere I would like to have this sanity checked from folks that know what they are doing. Are there any drawbacks?

Thanks

Florian